OpenLane Architecture¶

OpenLane Design Stages¶

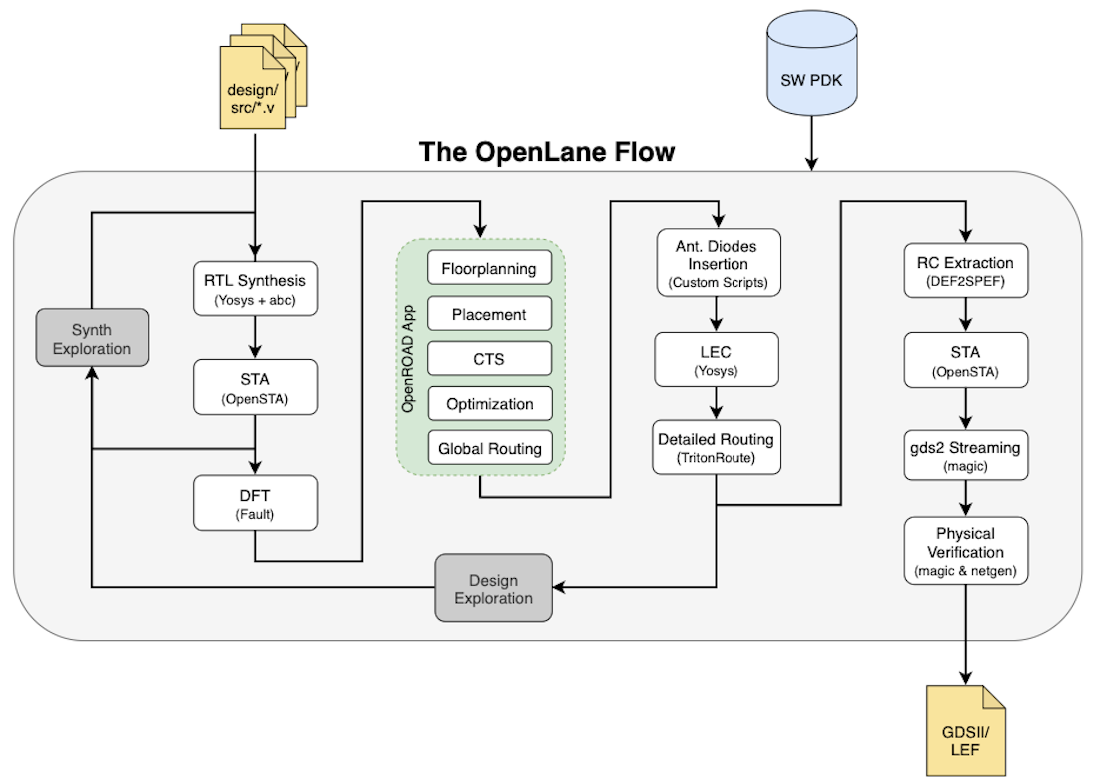

OpenLane flow consists of several stages. By default all flow steps are run in sequence. Each stage may consist of multiple sub-stages. OpenLane can also be run interactively as shown here.

Synthesis

yosys/abc- Perform RTL synthesis and technology mapping.OpenSTA- Performs static timing analysis on the resulting netlist to generate timing reports

Floorplaning

init_fp- Defines the core area for the macro as well as the rows (used for placement) and the tracks (used for routing)ioplacer- Places the macro input and output portspdngen- Generates the power distribution networktapcell- Inserts welltap and decap cells in the floorplan

Placement

RePLace- Performs global placementResizer- Performs optional optimizations on the designOpenDP- Performs detailed placement to legalize the globally placed components

CTS

TritonCTS- Synthesizes the clock distribution network (the clock tree)

Routing

FastRoute- Performs global routing to generate a guide file for the detailed routerTritonRoute- Performs detailed routingOpenRCX- Performs SPEF extraction

Tapeout

Magic- Streams out the final GDSII layout file from the routed defKLayout- Streams out the final GDSII layout file from the routed def as a back-up

Signoff

Magic- Performs DRC Checks & Antenna ChecksKLayout- Performs DRC ChecksNetgen- Performs LVS ChecksCVC- Performs Circuit Validity Checks

OpenLane integrated several key open source tools over the execution stages:

RTL Synthesis, Technology Mapping, and Formal Verification : yosys + abc

Static Timing Analysis: OpenSTA

Placement: RePLace (Global), Resizer and OpenPhySyn (formerly), and OpenDP (Detailed)

Clock Tree Synthesis: TritonCTS

Fill Insertion: OpenDP/filler_placement

Routing: FastRoute or CU-GR (formerly) and TritonRoute (Detailed) or DR-CU

SPEF Extraction: OpenRCX or SPEF-Extractor (formerly)

LVS check: Netgen

Antenna Checks: Magic

Circuit Validity Checker: CVC

Everything in Floorplanning through Routing is done using OpenROAD and its various sub-utilities.

OpenLane Output¶

All output run data is placed by default under ./designs/design_name/runs. Each flow cycle will output a timestamp-marked folder containing the following file structure:

<design_name>

├── config.json/config.tcl

├── runs

│ ├── <tag>

│ │ ├── config.tcl

│ │ ├── {logs, reports, tmp}

│ │ │ ├── cts

│ │ │ ├── signoff

│ │ │ ├── floorplan

│ │ │ ├── placement

│ │ │ ├── routing

│ │ │ └── synthesis

│ │ ├── results

│ │ │ ├── final

│ │ │ ├── cts

│ │ │ ├── signoff

│ │ │ ├── floorplan

│ │ │ ├── placement

│ │ │ ├── routing

│ │ │ └── synthesis

To delete all generated runs under all designs:

make clean_runs